## SOLID FADC test status and plan

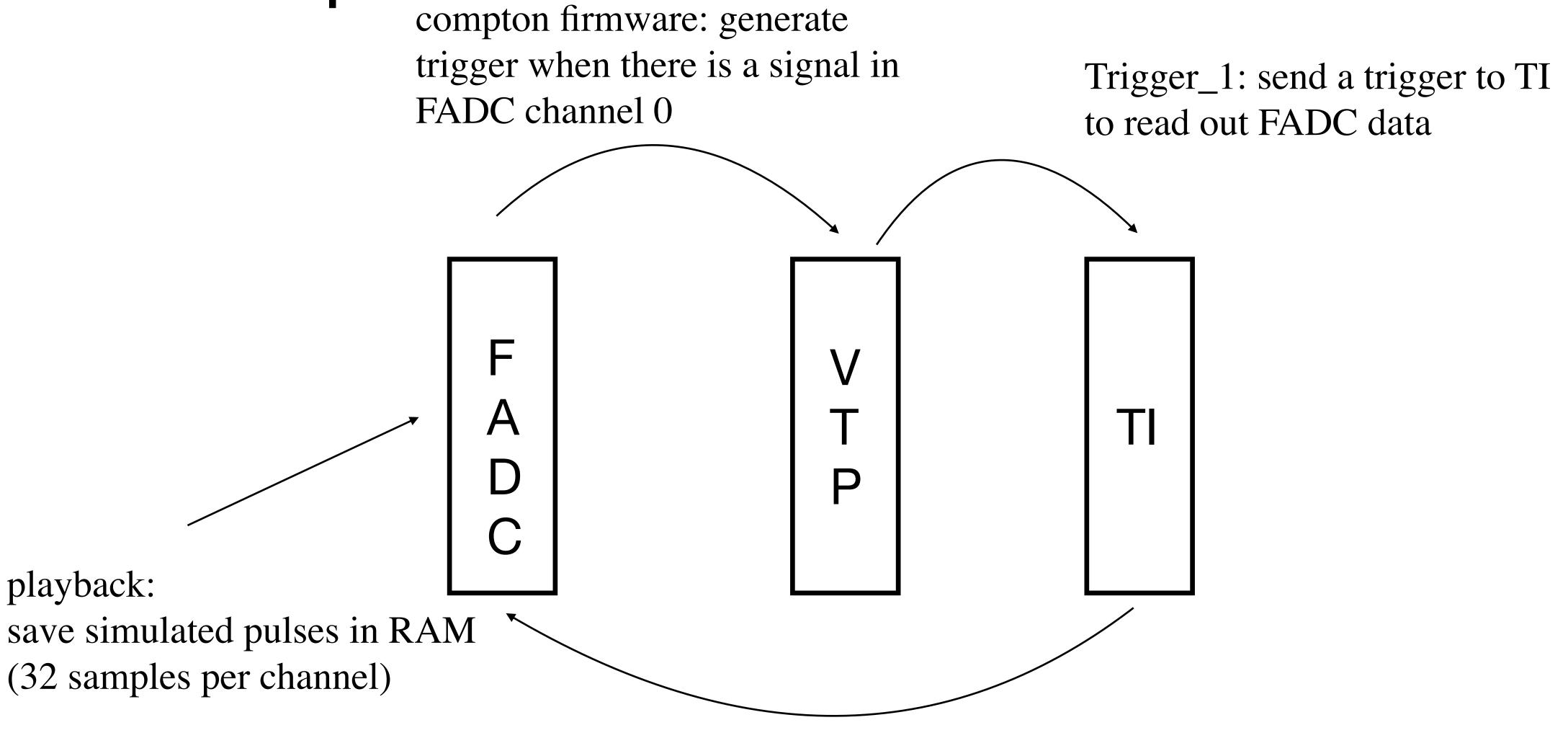

## **Test stand setup**

Trigger\_2: TI internal pulser generates a Trigger\_2 type trigger which injects the simulated data in the FADC

(Event rate can be controlled here)

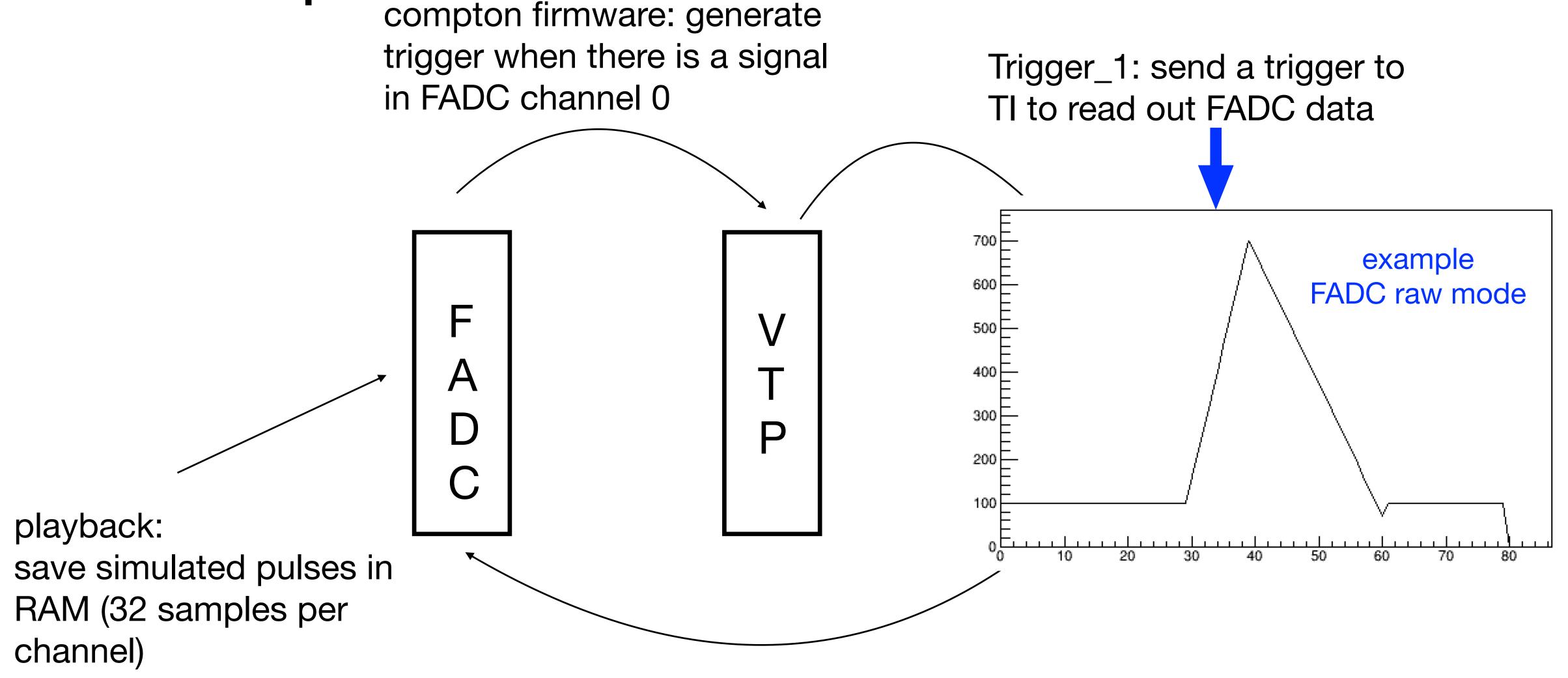

## **Test stand setup**

Trigger\_2: TI internal pulser generates a Trigger\_2 type trigger which injects the simulated data in the FADC

(Event rate can be controlled here; rate = 500kHz/2^n, n=0-15)

## FADC dead time measurement plan

- Ben is going to update the FADC firmware to allow part of the FADC channels can accept analog input

- Send MPS signals from the helicity board to FADC so the scalers in VTP can be enabled

- With 16 FADC channels enabled, set the random pulser rate (500kHz/2^n) to:

- n=8, rate = 1.95 kHz

- n=6, rate = 7.81 kHz

- n=5, rate = 15.625 kHz

- n=4, rate = 31.25 kHz

- n=3, rate = 62.5 kHz

- n=2, rate = 125 kHz

- n=1, rate = 250 kHz

- Measure the FADC dead time as (1 FADC\_counts/scaler\_counts)